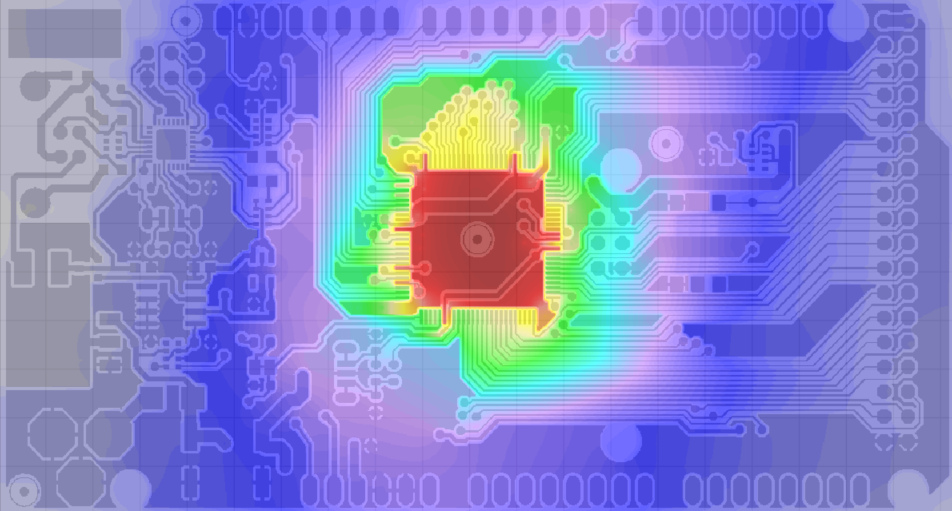

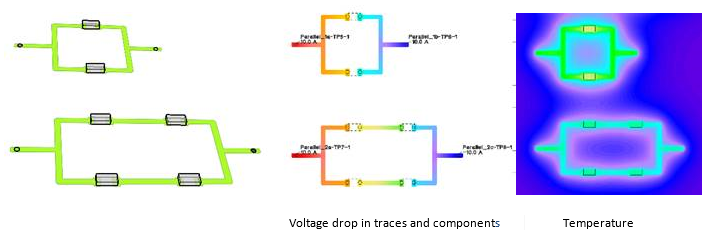

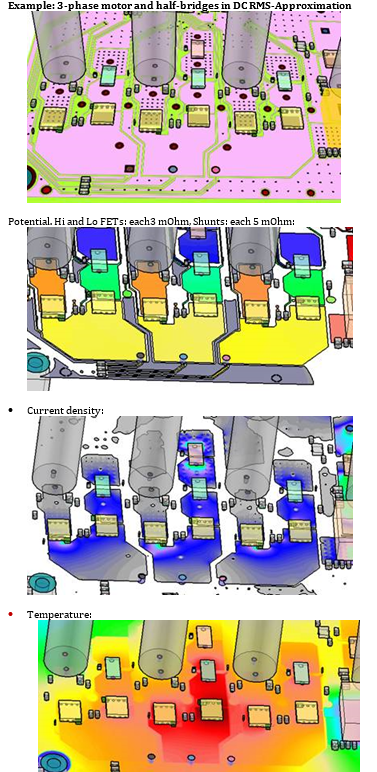

Leiterplatten mit vielen Lagen, feiner x-y Auflösung oder große "Kuchenbleche" stellen numerisch eine Herausforderung dar. Bisher war es so: je mehr Berechnungsknoten zu lösen waren, desto mehr Iterationen wurden benötigt und es war nicht unwahrscheinlich, dass es zu instabiler Konvergenz kam (die durch internen Korrekturmechanismen abgefangen wurde).

Mit Release TRM3.6 kommt ein neuer "Turbo"-Algorithmus dazu, der das 3D Temperaturfeld ca. 10x schneller als bisher löst. Durch aktivieren des Multi-threading lässt sich evtl. noch mehr herausholen. Wirklich anspruchsvolle Projekte laufen jetzt innerhab von einigen 10 Minuten, anstatt einer oder mehreren Stunden durch.

Eine Testinstallation beantragen Sie hier